1259 search results - page 159 / 252 » Efficient Wire Formats for High Performance Computing |

145

click to vote

ICS

2009

Tsinghua U.

15 years 11 months ago

2009

Tsinghua U.

In this work, we propose a new FPGA design flow that combines the CUDA programming model from Nvidia with the state of the art high-level synthesis tool AutoPilot from AutoESL, to...

145

click to vote

ESTIMEDIA

2009

Springer

15 years 2 months ago

2009

Springer

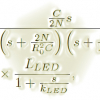

The increasing demand for low power and high performance multimedia embedded systems has motivated the need for effective solutions to satisfy application bandwidth and latency req...

162

click to vote

WWW

2008

ACM

16 years 5 months ago

2008

ACM

Web search engines are facing formidable performance challenges due to data sizes and query loads. The major engines have to process tens of thousands of queries per second over t...

276

click to vote

ASPLOS

2009

ACM

16 years 5 months ago

2009

ACM

QR decomposition is a computationally intensive linear algebra operation that factors a matrix A into the product of a unitary matrix Q and upper triangular matrix R. Adaptive sys...

254

click to vote

Publication

Efficient bandwidth allocation and low delays remain important goals, expecially in high-speed networks. Existing end-to-end congestion control schemes (such as TCP+AQM/RED) have s...