684 search results - page 70 / 137 » Techniques for low energy software |

DAC

2006

ACM

16 years 24 days ago

2006

ACM

The increasing use of Multiprocessor Systems-on-Chip (MPSoCs) for high performance demands of embedded applications results in high power dissipation. The memory subsystem is a la...

CODES

2007

IEEE

15 years 6 months ago

2007

IEEE

In this paper we present an approach to the scheduling and voltage scaling of low-power fault-tolerant hard real-time applications mapped on distributed heterogeneous embedded sys...

108

click to vote

GLVLSI

2005

IEEE

15 years 5 months ago

2005

IEEE

The instruction cache is a popular target for optimizations of microprocessor-based systems because of the cache’s high impact on system performance and power, and because of th...

BSN

2009

IEEE

15 years 6 months ago

2009

IEEE

—A biomonitoring application running on wireless BAN has stringent timing and energy requirements. Developing such applications therefore presents unique challenges in both hardw...

ISBI

2008

IEEE

16 years 17 days ago

2008

IEEE

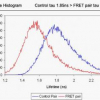

Studying cellular protein-protein interactions in situ requires a technique such as fluorescence resonance energy transfer (FRET) which is sensitive on the nanometer scale. Observ...